# **Serial Data Hub**

Project Plan

Senior Design Group DEC13-13 Team members: Steven LeBlanc, Adriana Ceylan, Darin Cleveland, Justin Wheeler Advisor: Dr. Arun Somani Client: Dr. Koray Celik

# Table of Contents:

| Introduction and Problem Statement:              |    |

|--------------------------------------------------|----|

| Objective and System Description:                | 3  |

| Functional Requirements:                         | 3  |

| Non Functional Requirements:                     | 3  |

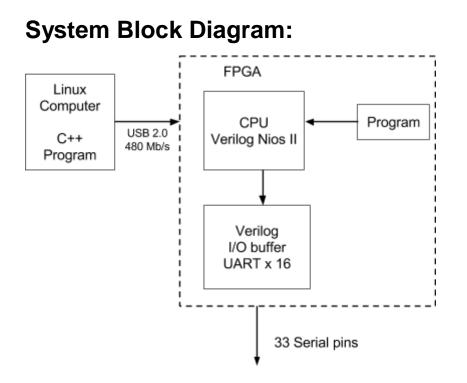

| System Block Diagram :                           | 4  |

| Assumptions/Design Choices/Operation Conditions: | 4  |

| Material List:                                   | 5  |

| Justification for Materials:                     | 5  |

| Researched Options:                              | 5  |

| Deliverables:                                    | 7  |

| Constraints:                                     | 7  |

| Risks/Challenges:                                | 8  |

| General Timeline/Work Breakdown:                 | 9  |

| Cost Breakdown:                                  | 10 |

#### **Introduction and Problem Statement:**

Members of an Iowa State research team are developing autonomous robots to map floor plans of an unknown building. For any robotics development, debugging requires sending and gathering data with a component. There exist many one-to-one signal conversion products; however, they would each run independent of each other and would destabilize the synchronization of data. For assistance in their robotics development, they require a tool to serially communicate with multiple components of the robot at once. For this, Dr. Koray Celik, has requested that we build a serial data hub to connect a laptop to sixteen different serial devices.

## **Objective and System Description:**

Our objective is to build a serial data hub. The peripheral will be a separate module that connects to a Linux laptop by a USB cable and then connects to sixteen other serial ports on various robotics components of a machine. The hardware logic will be implemented on an Altera Cyclone II FPGA mounted on a PCB board with RS-232 connectors. The FPGA will run firmware with Altera's Nios II soft-core processor. Communication will be handled via an API on a laptop running Ubuntu v11.04.

### **Functional Requirements:**

- System must provide multiple serial port interfaces to connect robotics peripheral components

- System must provide a serial port interface to connect to controlling PC

- System must transfer data between PC and component in a way that ensures no data is lost (guarantees data integrity)

- System must manage 16 to 1 data throughput channels

- System must transfer data in a prompt manner to reflect real-time systems

- System must be controlled by an API library on the PC

### **Non Functional Requirements:**

- System shall implement an Altera Nios II soft processor.

- System shall use the soft processor to run firmware code on FPGA.

- System shall be prototyped on Altera's DE2 Development Board

- System shall use USB 2.0 to communicate between the FPGA and the PC API.

- System shall use same USB controller as the DE2 Board

- System shall have 16 serial ports implementing RS-232 on DB9 connectors

- System shall use external memory modules rather than FPGA memory

## **Assumptions/Design Choices/Operation Conditions:**

-Will be running an Altera Nios II soft processor on an Altera Cyclone II FPGA

-Will be using no parity check on UART

-Will assume serial components follow UART capabilities

-Will be using memory hardware external to the FPGA

-Will be using the USB controller akin to the one on the DE2 board

-End product will be needed in an end application for ground robots.

-API support is guaranteed for, but not limited to, Ubuntu 11.04. Drivers may or may not work on other operating systems.

-Will be using Altera's DE2 development board for prototyping.

## **Material List:**

Below is a list of hardware and software materials and tools that will be used for the project.

#### Hardware:

-Altera Cyclone II FPGA development board (DE2) -Laptop with Linux Ubuntu v11.04

#### Software:

-Altera Quartus II:

A licensed Altera software tool used for analysis and synthesis of hardware descriptive language (HDL) design. This program enables the developer to compile their design, perform timing analysis, simulate designs and configure the target device.

-ModelSim:

A licensed software tool that help simulates, compiles, and debugs VHDL or Verilog designs without loading the design on a FPGA.

-MegaCore Library:

A licensed library for the Altera Quartus II software. This library contains a list of likened Altera cores. The Nios II embedded soft processor is located in this library.

#### **Justification for Materials:**

We decided to use an FPGA so that we could have access to a large number of programmable GPIO pins to support a large number of ports. The group decided to use an Altera Cyclone II DE2 development board which includes many useful hardware components already on it and it was a platform our group had familiarity with. Instead of programming hardware logic into the FPGA or using a pre-made processor, the group decided to use an Altera Nios II soft processor on our FPGA for easier modification at a later date

## **Researched Options:**

There were two main options to approach this project. We could use a microcontroller and add supporting UART chips, and USB controller. The second option is that we could use an FPGA/development board and design hardware logic and firmware.

We chose to not use a microcontroller due to the lack of included UART modules and the lack of general IO pins available. Additionally we would not be able to guarantee synchronized buffering between the separate UART modules.

Below is the breakdown of research of each option.

#### 1. Microcontroller with supporting chips

| Items:                                          | Descriptions/Features:                                                                                                                                                                                                                                                                                                                                                                                    | Cost:                    |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| Arduino Mega<br>2560                            | <ul> <li>ATmega2560 microcontroller (256 KB flash memory)</li> <li>54 digital input/output pins (16 analog, 15 with PWM)</li> <li>4 UARTs (hardware serial ports)</li> <li>clock speed 16 MHz</li> <li>USB connection</li> </ul>                                                                                                                                                                          | \$55.56                  |

| Atmel<br>Microprocessor:<br>AT91SAM7S512        | <ul> <li>Flash (Kbytes):512 Kbytes</li> <li>Pin Count:64</li> <li>Max. Operating Freq. (MHz):55 MHz</li> <li>CPU: ARM7TDMI</li> <li>Max I/O Pins:32</li> <li>USB Transceiver:1</li> <li>USB Speed: Full Speed</li> <li>USB Interface: Device</li> </ul>                                                                                                                                                   | \$16.54                  |

| UART Chips:<br>Texas<br>Instrument:<br>PC16550D | <ul> <li>FIFO mode transmitter and receiver are each buffered with 16 byte</li> <li>Fully programmable serial-interface characteristics:         <ul> <li>5-, 6-, 7-, or 8-bit characters</li> <li>Even, odd, or no-parity bit generation and detection</li> <li>1-, 1½-, or 2-stop bit generation</li> <li>Baud generation (DC to 1.5M baud).</li> </ul> </li> <li>False start bit detection.</li> </ul> | 16 x \$7.55<br>=\$120.80 |

| USB Controller:<br>Philips ISP1362              | <ul> <li>Data transfer at full-speed (12 Mbit/s) and low-speed (1.5 Mbit/s)</li> <li>Controllable LazyClock (110 kHz ± 50 %) output during 'suspend'</li> <li>Operates at 3.3 V power supply</li> <li>12 MHz crystal or direct clock source with on-chip Phase-Locked Loop (PLL)</li> <li>16-bit data bus</li> <li>10 Mbyte/s data transfer rate between the microprocessor and ISP1362</li> </ul>        | \$6.45                   |

#### 2. FPGAs/Development Boards

| Items:                                                                 | Descriptions/Features:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Cost: |

|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Xilinx Zynq-7000<br>All<br>Programmable<br>SoC ZC702<br>Evaluation Kit | <ul> <li>16MB Quad SPI Flash</li> <li>DDR3 Component Memory 1GB</li> <li>Support 32 data width</li> <li>USB OTG 1 (PS) - Host USB</li> <li>USB UART (PS)</li> <li>12V wall adapter or ATX</li> <li>33.33MHz Fixed PS System Oscillator (Single-<br/>Ended CMOS)</li> <li>FMC #1-LPC connector (0 GTX Transceiver, 68<br/>single-ended or 34 differential user defined signals)</li> <li>FMC #2-LPC connector (0 GTX Transceiver, 68<br/>single-ended or 34 differential user defined signals)</li> </ul> | \$895 |

| Altera Cyclone II<br>DE2<br>(chosen option)                            | <ul> <li>Built-in USB-Blaster for FPGA configuration</li> <li>USB 2.0 (type A and type B)</li> <li>Expansion headers (two 40-pin headers)</li> <li>Memory: 8 MB SDRAM, 512 KB SRAM, 4 MB<br/>Flash</li> <li>Clock options: 50 MHz clock or 27 MHz</li> </ul>                                                                                                                                                                                                                                             | \$269 |

### **Deliverables:**

- Either a PCB or a DE2 board containing an Altera Cyclone II FPGA loaded with a custom Nios II processor and firmware.

- Quartus project files for custom Nios II processor

- Verilog code for custom hardware module

- Firmware code to run on the soft processor

- Interconnect Schematics and System Block Diagrams

- Device Driver and API for Ubuntu 11.04 Linux Laptop

# **Constraints:**

Time - The project must be completed by the end of the Fall 2013 semester.

**Budget** - While no specific amount has been set in stone, we are expected to limit our expenditures as much as possible. Many of the materials needed have been supplied by the client, including a DE2 board.

# **Risks/Challenges:**

Below is a list of potential risks and solutions that may occur during the life cycle of the project.

| Potential Risks                                               | Solutions                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| If the group loses a member, how will tasks be redistributed? | Each team member was given a responsibility<br>for each of their components. If for any reason<br>one member leaves, that person's task will be<br>given to the team member with the most<br>experience in the area of the task and/or the<br>team member with the lesser amount of tasks.                                                                                              |

| If no access to software licenses?                            | First contact CSG or Jason Boyd (ISU Altera<br>Contact) if a license could be obtained. Then<br>contact the company responsible (Altera, SLS,<br>etc) to see if a license could be provided. Third<br>option is looking into Open Core<br>software/design, or opinion of advisor and/or<br>client.                                                                                      |

| If hardware fails/broken?                                     | If there is a hardware issue, first verify it is not a<br>software problem by testing with other DE2<br>boards (either in lab 2051 or borrow a board<br>from the parts shop). If indeed a hardware<br>problem, contact advisor to see if a part could<br>be replace or contact Jason Boyd to see if an<br>extra DE2 board could be borrowed until<br>another DE2 board can be purchase. |

| If an unexpected bug/error occurs during integration?         | Identify the component the bug/error is related<br>to, then replicate the error and debug/test the<br>individual component. Most likely the team<br>member most familiar with the component would<br>lead or assist the debugging process.                                                                                                                                              |

| If a problem occurs for final demo?                           | Have a back-up board/demo ready. Maybe have<br>a video recording of a working demo that could<br>be displayed on a laptop.                                                                                                                                                                                                                                                              |

| If there is a code and documentation version control problem? | As a team we will have all our code and<br>documentation on Google Drive, as well as<br>Subversion or GIT. We will provide access of<br>version control depositary as part of<br>deliverables.                                                                                                                                                                                          |

# Initial Estimate of Timeline/Work Breakdown

Below is a list of tasks and estimated time, description, and task owner.

| Task                                 | Description                                                                                                                                                                            | Time<br>Estimate | Task Owner           |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|

| UART Clk<br>Divider                  | Design clock divider to go inside the UART receiver in Verilog. Design and run testbenches in simulation.                                                                              | 1 week           | Darin and<br>Adriana |

| UART Shifter                         | Design bit shifter to go inside the UART receiver in Verilog. Design and run testbenches in simulation.                                                                                | 1 week           | Darin and<br>Adriana |

| UART FIFO                            | Design the FIFO module for the UART receiver.<br>Design and run testbenches in simulation.                                                                                             | 1 week           | Darin and<br>Adriana |

| UART RX<br>module                    | Combine clock divider, bit shifter, and FIFO<br>with miscellaneous control logic to create the<br>receiver module for the UART. Design and run<br>testbenches in simulation.           | 1 week           | Darin and<br>Adriana |

| UART TX<br>module                    | Copy the receiver module and then modify the direction of some bit streams to create the UART transmitter. Design and run testbenches for simulation.                                  | 1 week           | Darin and<br>Adriana |

| UART<br>Monkey<br>Testing            | Detailed Testing of UART                                                                                                                                                               | 2 weeks          | Darin                |

| Get API Req                          | Need to contact Koray to get specific API requirements for the C modules                                                                                                               | 1 week           | Justin               |

| Write Header<br>Files                | Write header files for API. Determine function return values and function parameters.                                                                                                  | 1 week           | Justin               |

| Write Simple<br>USB Test<br>Program  | Based on initial research, USB supports a command that will identify a device connected to one of its ports. Write a test program that does just this.                                 | 2 weeks          | Justin               |

| Upload basic<br>Nios II<br>processor | Upload a simple version of the Nios II<br>processor to one of the Altera Cyclone FPGA's.<br>Write a simple C program for the processor.<br>Upload and run the program off of the FPGA. | 2 weeks          | Steven               |

| Store data<br>from 17<br>locations into<br>2 buffers | Design the logic channels for communication<br>between the 16 + 1 ports and the buffers for<br>holding data          | 1 week  | Steven                |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------|-----------------------|

| Firmware<br>Interrupts                               | Implement an interrupt system for Firmware to send back to USB                                                       | 2 weeks | Steven and<br>Adriana |

| External<br>Memory<br>Modules                        | Develop interface to external memory modules with the Nios II processor or the firmware                              | 3 weeks | Steven and<br>Adriana |

| Interface with<br>USB controller                     | DE2 board has an interface chip that controls<br>the USB ports whether the FPGA is acting as a<br>host or peripheral | 2 weeks | Steven and<br>Justin  |

| Interface with<br>UART module                        | Need to connect UART module to the Nios II processor.                                                                | 1 week  | Adriana and<br>Steven |

| CRC Error<br>Correction                              | Implement Error Correction System                                                                                    | 1 week  | Steven and<br>Justin  |

#### **Cost Breakdown**

There are two paths our group can take in order to produce the final product. Option one is to design keeps the design on the DE2 board, and option two is to place the final design on a PCB.

| DE2 Final Product Option | Cost       | PCB<br>Final<br>Project<br>Option | Cost   |

|--------------------------|------------|-----------------------------------|--------|

| DE2 board                | \$269      | PCB (5<br>units)                  | ~\$150 |

| GPIO Connectors          | ~\$7.95    | Cyclone<br>II FPGA                | \$150  |

| D89 Connectors (8 units) | ~\$40      | Max232<br>(16 units)              | ~\$5   |

|                          |            | Voltage<br>Regulator              | \$70   |

| Total Cost:              | *~\$316.95 | Total<br>Cost:                    | ~\$375 |

\*note: DE2 option is effectively only ~\$47.95, since the client already has a spare DE2 board to be used.